3.1.1 소자 제조

반도체 소자의 제조는 대부분의 반도체 제조 회사에서 Si(실리콘) 웨이퍼를 구매하는 것으로 시작됩니다. 대형 반도체 공장은 하나의 Si 웨이퍼를 40,000개 이상 처리할 수 있는 능력을 가지고 있습니다.

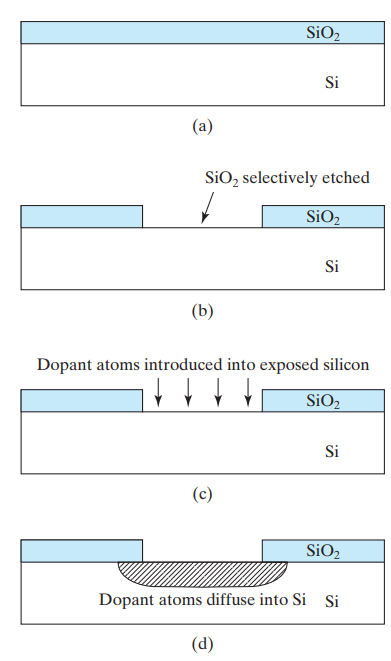

간단하게 말하면 반도체 소자 제조 공정은 다음과 같습니다:

- SiO2 형성: 먼저 Si 웨이퍼에 이산화규소(SiO2)를 형성합니다.

- 산화물의 선택적 제거: 형성된 산화물 중에서 필요한 부분만 선택적으로 제거합니다.

- 도펀트 주입: 웨이퍼 표면에 도펀트(불순물)를 주입합니다.

- 도펀트 확산: 도펀트를 웨이퍼 내로 확산시킵니다.

이러한 단계들과 다른 제조 단계들을 조합하여 반도체 소자와 회로를 만들어냅니다. 웨이퍼 기판 위에 층층이 회로를 만드는 이러한 방법을 평면 기술(Planar Technology)이라고 합니다.

평면 기술의 이점 중 하나는 이를 Si 웨이퍼 전반에 적용할 수 있다는 것입니다. 이는 동일한 웨이퍼 크기에서 많은 회로 칩을 만들어내어 경제적인 이점을 가져다줍니다.

3.2.1 실리콘의 산화

실리콘의 산화물은 SiO2(이산화규소)입니다. SiO2는 여러 목적으로 사용되는데, 그중 하나는 도펀트를 주입시킬 때 마스크 역할을 하는 것입니다.

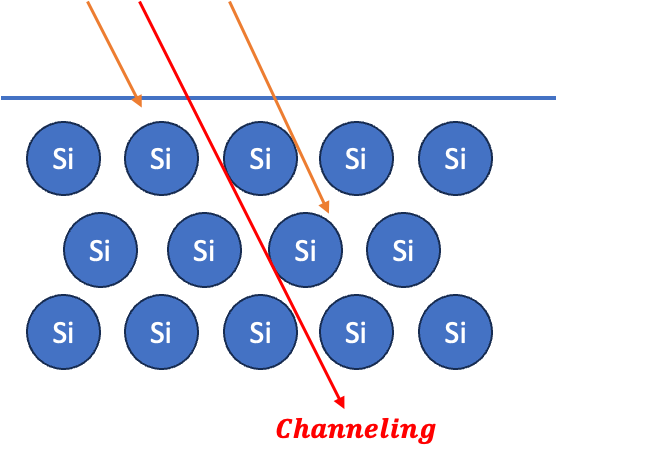

단결정 Si 표면 위에 도펀트 Implantation을 하게 되면 Si 결정 사이로 도펀트 원자가 원하지 않는 경로로 빠져나가는 Channeling 효과를 줄일 수 있습니다. 이는 SiO2 막질이 Si 결정보다 더 Amorphous 하기 때문에 가능합니다.

SiO2는 실리콘 MOSFET에 필수적입니다. FET(Field Effect Transistor)를 구현하기 위해 Metal과 Si 사이에 절역막은 필수이며, SiO2가 주로 사용됩니다. 또한, 여러 Layer로 구성된 배선에서 서로 다른 Metal Layer가 붙어서 Short가 나지 않도록 하기 위해 절연막으로도 사용됩니다.

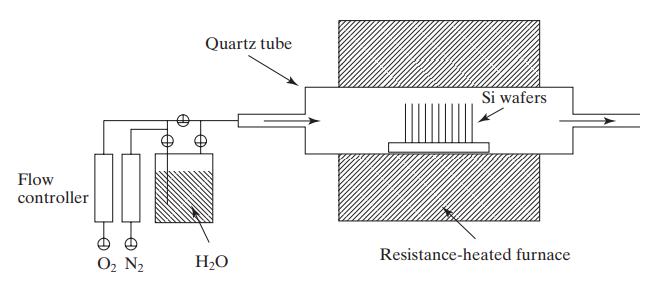

SiO2를 만드는 방법은 크게 건식(Dry)과 습식(Wet)으로 나뉩니다. 건식은 Si에 O2 가스를 사용하고 높은 온도에서 성장시킵니다. 일반적으로 얇은 막을 형성할 때 사용되며, 좋은 품질의 산화물을 생성합니다. 습식은 Si에 O2 대신 H2O를 사용하며, H2O가 O2보다 빠르게 SiO2를 통과하고 확산되므로 두꺼운 산화물을 형성할 때 주로 사용됩니다. 습식 방식은 더 빠른 산화물 생성을 가능케 하며, 산화는 일반적인 증착(Deposition)과는 달리 Si와 반응하여 성장하므로 Si 표면을 어느 정도 소모합니다.

3.3.1 포토리소그래피 (Photolithography)

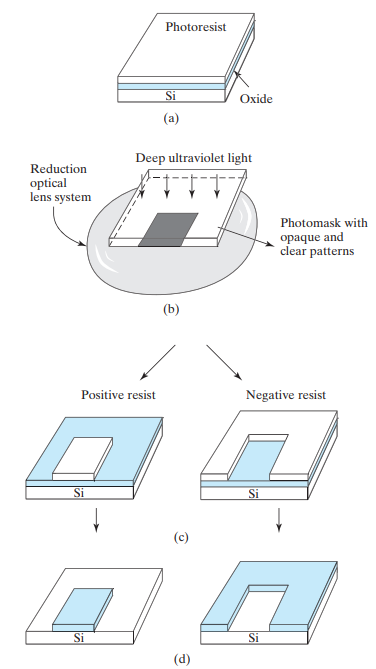

포토리소그래피는 반도체 구조물을 만들기 위한 핵심 공정 중 하나로서, 쌓고(Deposition) 깎는(Etching) 과정을 반복합니다. 이 과정에서 얻은 원하는 패턴을 만들기 위해서는 선택적으로 깎아야 하는데, 포토리소그래피는 빛을 이용하여 빛을 받은 부분을 깎거나, 안 받은 부분을 깎을 수 있게 합니다. 이는 사진 인화 방식과 유사합니다.

a. HDMS Coating

- 먼저, HDMS를 Spit Coater로 균일하게 발라줍니다. Spin Coater를 사용하여 Si 웨이퍼를 고정하고 액체를 도포한 후 웨이퍼를 회전시켜 액체를 균일하게 퍼뜨립니다.

- HDMS는 Si의 표면을 소수성으로 만들어주어 소수성인 포토레지스트와의 접착력을 향상합니다.

b. Spin Coat (PR)

- 포토레지스트는 폴리머로, 빛에 반응하여 선택적으로 남을 수 있는 물질입니다. PR은 폴리머, 감광 물질, 용매로 구성되어 있습니다.

- HDMS 코팅 후 동일하게 포토레지스트(PR)를 Spin Coater로 코팅합니다.

c. Soft Bake

- 다음으로, 90도 정도에서 Baking을 하여 고체 폴리머만 남도록 용매를 날려줍니다.

d. Exposure

- 그 후, 빛을 광 마스크(Photo Mask)를 통해 PR에 쏴주어 패턴을 만듭니다(노광). Photo Mask는 빛이 투과되는 부분과 그렇지 않은 부분을 만들어 원하는 패턴에만 빛이 쏴지도록 합니다.

- 노광 후, 빛을 받은 PR 부분은 감광제 물질로 인해 화학 작용이 변경됩니다.

e. Develop

- (Positive 기준으로) 빛을 받은 포토레지스터 부분은 현상액(Developer)을 통해 씻겨나갑니다.

f. Hard Bake

- 현상 후, Bake를 통해 남은 용매를 날려주고 PR을 단단하게 합니다.

- 원하지 않는 막을 제거하기 위해 노출된 PR 막 위에 용액(Etchant)나 Dry Etch를 사용하여 제거합니다.

g. Strip

- 패턴화 된 PR 사이로 충분한 막이 제거되었다면, 불 필요한 PR을 제거(strip)합니다. Strip은 화학 용액을 사용하여 제거하거나, 산소 플라스마나 UV 오존 시스템을 사용하여 물리적으로 Ashing 하는 방법이 있습니다.

3.3.2 습식 리소그래피 (Immersion Lithography)

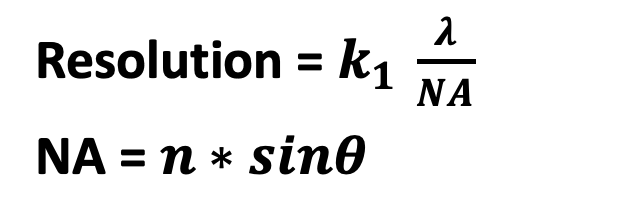

반도체 미세화에 따라 포토리소그래피의 Resolution을 높이기 위해 습식 리소그래피가 도입되었습니다. Resolution은 패턴을 얼마나 작게 만들 수 있는 능력을 나타내며 파장(λ)에 반비례하고 Numerical Aperture(NA)에 반비례합니다. 여기에서는 습식 리소그래피의 원리와 이점에 대해 설명하겠습니다.

- Resolution과 NA:

- Resolution은 λ/NA로 표현되며, λ는 빛의 파장을 나타냅니다.

- Numerical Aperture (NA)는 렌즈의 크기에 관련된 파라미터로서, NA가 높을수록 더 낮은 파장에서 더 높은 Resolution을 달성할 수 있습니다.

- 공정에 사용되는 고정 NA는 공정 상수 k1과 λ에 비례합니다

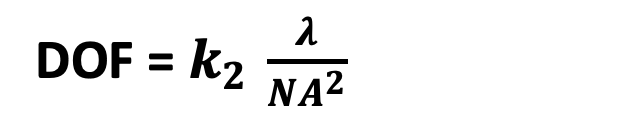

- Depth of Focus (DOF):

- Depth of Focus (DOF)는 초점 거리에 영향을 미치는 파라미터로, 렌즈의 초점을 얼마나 유지할 수 있는지를 나타냅니다.

- DOF는 λ에 비례하고 NA^2에 반비례합니다. 즉, DOF가 높으면 렌즈의 초점을 유지하기 쉬워집니다.

- NA를 높이는 방법:

- NA를 향상해 Resolution을 향상하는 방법 중 하나는 굴절률(n)을 활용하는 것입니다.

- 공기의 굴절률은 1이고, 물의 굴절률은 1.43입니다. 물은 공기보다 굴절률이 높기 때문에 렌즈와 마스크 사이에 물을 채우면 굴절률이 증가합니다.

- 높아진 굴절률은 더 작은 λ를 사용하여 더 작은 Resolution을 가능케 하며, 이 방식을 습식 리소그래피라고 합니다.

- 습식 리소그래피의 장점:

- 습식 리소그래피를 사용하면 렌즈와 마스크 사이에 물을 채우어 굴절률을 높이는 것으로써 고해상도를 달성할 수 있습니다.

- 공기보다 굴절률이 높은 물을 사용하면 더 작은 λ에서 고해상도를 유지할 수 있어, 미세한 패턴을 높은 품질로 제작할 수 있습니다.

3.3.3 전자 리소그래피 (Electron Beam Lithography)

전자 현미경의 해상도가 광학 현미경보다 뛰어나기 때문에 포토리소그래피보다 높은 해상도를 갖습니다. 전자 레지스트에 전자 빔을 조사하여 레지스트를 감광시키고, 패턴을 형성합니다. 하지만 전자 리소그래피는 일일이 전자를 쏴줘야 하기 때문에 Throughput이 떨어지는 단점이 있습니다.

3.3.4 나노임프린트(Nanoimprint)

나노임프린트는 고해상도의 광학 및 전자 리소그래피의 높은 비용을 극복하기 위한 방법 중 하나입니다. 패턴화 된 도장에 레지스트를 찍어내어 반복적으로 사용할 수 있습니다. 일부 고밀도 및 정밀한 애플리케이션에서 사용되며, 저렴한 제작 비용으로 높은 해상도를 달성할 수 있습니다.

3.4.1 에칭 (Etching)

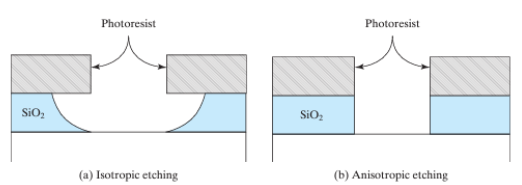

에칭은 포토리소그래피를 사용하여 만든 패턴대로 막질을 깎는 작업으로, 반도체 제조 공정에서 중요한 단계 중 하나입니다. 에칭은 등방성(Isotropic) 에칭과 이방성(Anisotropic) 에칭으로 나뉘며, 각각 다른 특성을 가지고 있습니다.

1. Wet Etch (습식 에칭):

Wet Etch에서는 용액을 사용하여 화학적이나 물리적으로 에칭이 이루어집니다.

예를 들어, SiO2를 깎을 때는 HF (Hydrogen Fluoride)가 사용되며, 이것은 등방성 에칭입니다.

등방성 에칭은 모든 방향으로 동일하게 깎이기 때문에, 원하는 패턴을 만들 때 유용합니다.

2. Dry Etch (드라이 에칭):Dry Etching은 플라즈마 상태에서 발생하는 이온, 전자, 원자, 라디컬이 포토레지스트와 노출된 SiO2와 화학적으로 반응하여 에칭이 이루어집니다.

드라이 에칭은 이방성 에칭이므로 특정 방향으로만 깎입니다.

이것은 등방성 에칭과 달리, 좀 더 정교한 패턴을 형성할 수 있게 합니다.

3. End Point Detector (EPD):

에칭의 적절한 정지 시점을 파악하는 데 중요한 역할을 하는 장치가 EPD입니다.

EPD는 에칭 중 발생하는 잔여물의 파장을 검출하여 에칭이 완료된 시점을 감지합니다.

에칭이 과하게 되면 불필요한 막질이 제거되어 회로의 손상이 발생할 수 있습니다.

4. Plasma Damage와 안테나 효과:

드라이 에칭에서는 플라즈마를 사용하므로 Plasma Damage에 주의해야 합니다.

Plasma 상태에서 발생하는 이온들은 전도체에 충전을 유발할 수 있습니다.

충전이 과도하면 얇은 산화물 사이에 높은 전압이 발생하여 산화물이 Break Down될 수 있습니다.

안테나 효과는 큰 전하들이 큰 전도체를 통해 얇은 산화물을 Break Down시키는 현상을 나타냅니다.

에칭은 반도체 제조에서 필수적인 단계이며, 정확한 제어가 요구되므로 공정 과정에서의 감시와 조절이 중요합니다.

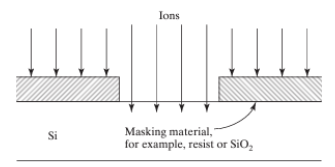

3.5.1 이온 주입 (Ion Implantation)

이온 주입은 고도로 정밀한 반도체 제조 공정 중 하나로서 Dopant 이온 원자를 높은 에너지로 가속하여 반도체 기판에 주입하는 과정입니다. 이로써 소자의 전기적 특성을 정확하게 제어할 수 있습니다.

1. 이온 주입 원리:

Dopant 이온은 높은 에너지로 가속된 후 Si 표면에 충돌하여 Si 격자에 삽입됩니다. 주입된 이온은 Si 원자의 격자 자리를 대체하며, 이는 반도체의 전기 특성을 결정하는 데 활용됩니다. 모든 이온이 Si 격자에 위치하지는 않으며, 어닐(Anneal) 열처리로 손상을 회복하고 Dopant를 활성화합니다.

2. Dopant 활성화:

Dopant를 활성화시키기 위해 어닐(Anneal) 열처리를 진행합니다.활성화된 Dopant는 Donor 또는 Acceptor로 작용하여 반도체의 전기적 특성을 형성합니다.

3. 이온 주입 특징:

이온 농도는 가우시안 분포를 따르며, Dose(이온 양)와 Energy(에너지)는 주입 깊이를 결정합니다.주입 과정에서 웨이퍼 차징을 중성화시키기 위해 전자를 주입할 수 있습니다.

4. 채널링 효과(Channeling Effect):

결정 방향에 따라 이온 주입 깊이가 달라지는 채널링 효과가 발생할 수 있습니다.이를 줄이기 위해 주입 각도를 Tilting하거나 Amorphous한 Oxide 막을 사용합니다.

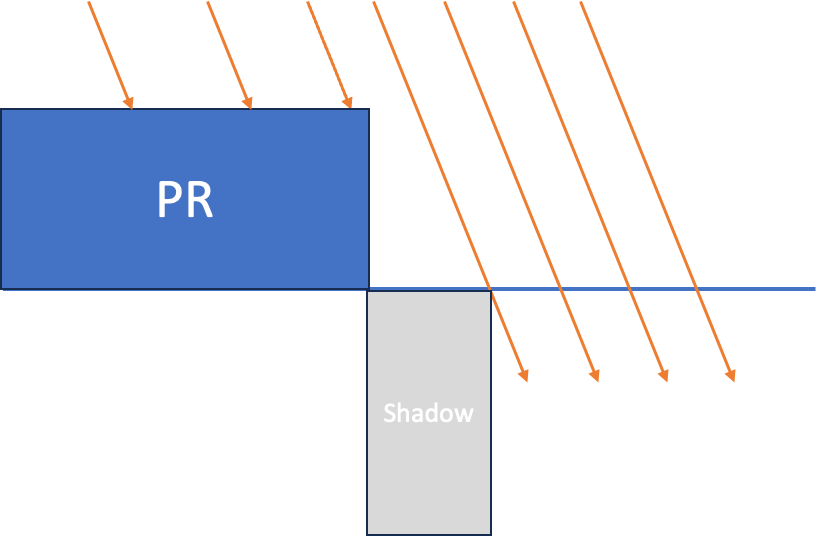

5. 그림자 효과(Shadow Effect):

패턴이 형성된 포토레지스트(PR)로 인해 발생하는 그림자 효과는 주입이 이뤄지지 않는 영역을 의미합니다.이를 해결하기 위해 주입 각도를 조절하여 그림자 부분까지 이온 주입을 진행합니다.

이온 주입은 반도체 소자의 정밀한 특성 제어를 위한 중요한 단계로, 정밀한 제어와 감시가 필수적입니다.

3.6.1 도펀트 확산 (Dopant Diffusion)

1. 도펀트 주입 방법:

도펀트를 실리콘(Si)에 효과적으로 주입하는 주요 방법은 이온 임플랜테이션을 통한 과정입니다. 때로는 Dopant를 더 깊게 밀어넣어야 할 필요가 있으며, 이때 사용되는 방법이 확산(Diffusion)입니다.

2. 확산 기본 원리:

Dopant를 주입한 후 Anneal(열처리)을 통해 확산을 진행합니다. Anneal로 인해 Dopant가 Si 격자 내에서 이동하며, 원하지 않는 깊이까지 확산될 수 있습니다. 확산 층의 두께는 Junction Depth로 표현되며, 이는 Dopant가 효과적으로 표면으로부터 얼마나 깊이 들어갔는지를 나타냅니다.

3. 확산 특징:

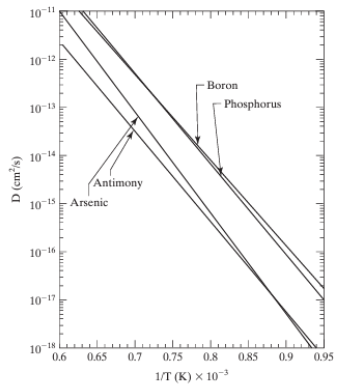

확산된 Dopant의 농도는 가우시안 분포를 따릅니다. 확산 비율은 온도가 증가함에 따라 증가하며, 일반적으로 900°C~1200°C 범위에서 이루어집니다. Dopant 확산은 Predeposition(소스 공급)과 Drive In(확산 진행) 단계로 나뉘어집니다.

4. Dopant 확산 온도 조절:

상온에서는 Dopant의 확산이 미미합니다. 고성능 소자에서는 얕은 확산이 필요하며, 이를 위해 높은 온도에서의 확산이 요구됩니다. Furnace Annealing은 일반적인 방법이지만, 낮은 온도에서는 시간이 오래 걸리고, Boron 같은 가벼운 Dopant의 경우 과도한 확산이 발생할 수 있습니다.

5. 온도 관련 문제와 해결책:

고온에서의 격자 손상은 빠르게 진행되나 손상이 어닐링되면 확산이 감소합니다.이러한 현상을 TED(Transient Enhanced Diffusion)이라고 합니다. 이 문제를 해결하기 위해 높은 온도에서 짧은 시간 동안 확산을 진행하는 방법이 제안되었습니다. Rapid Thermal Annealing(RTA) 및 레이저 펄스를 사용한 Laser Annealing이 빠른 열 전달과 높은 효율성으로 알려져 있습니다.

도펀트 확산은 반도체 소자의 특성을 높이기 위한 효과적인 단계로서, 온도와 시간을 효과적으로 관리하는 것이 중요합니다.

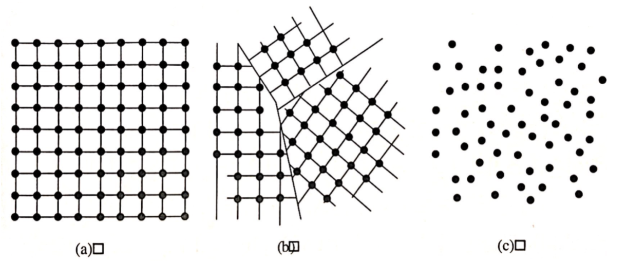

3.7.1 결정

고체 물질은 단결정(Crystalline), 다결정(Polycrystalline), 또는 비정질(Amorphous) 형태로 존재할 수 있습니다. 단결정은 완벽한 주기적 구조를 가지며, 다결정은 여러 부분적인 단결정인 Grain들이 모여 형성됩니다. 각 Grain은 10~10,000nm 크기를 가지며, 높은 온도에서 증착된 금속 박막과 Si 필름은 다결정에 속합니다. 또한, 다결정과 단결정 Si은 전기적 특성에서 유사합니다. 비정질 물질은 원자들이 정렬되어 있지 않으며, 낮은 온도에서 증착된 SiO2, SiN 그리고 Si는 이 범주에 속합니다. 비정질 및 다결정 Si의 이동도는 단결정 Si에 비해 낮습니다.

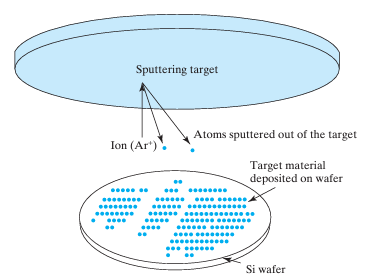

3.7.2 Sputtering

Sputtering은 PVD(Physical Vapor Deposition)의 한 형태로, 물리적으로 증착하는 과정입니다. 이 과정은 플라스마 상태에서 진행되며, Ar(Argon) 환경의 Chamber에서 진공이 형성된 후 일정 전압이 가해지면 플라스마 상태가 됩니다. 플라즈마 상태에서 Ar은 자유 전자와 이온이 생성되며, Ar 이온은 음의 전위로 가해진 Target으로 향해 이동하면서 Target 원자를 튕겨내어 Si 웨이퍼에 충돌시켜 증착됩니다. 도체의 경우 DC 전압을 사용하지만 절연막의 경우 RF 전압을 사용해야 합니다.

3.7.3 CVD(Chemical Vapor Deposition)

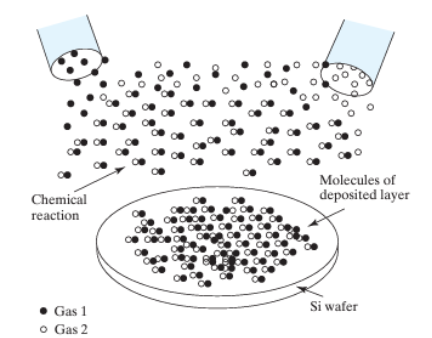

Sputtering은 방향성이 있어 수평 및 수직 표면에 대한 증착이 좋지 않지만, CVD를 활용하면 Conformal하게 증착할 수 있어 Step Coverage가 향상됩니다. CVD는 기체 성분을 이용하여 화합물이 분해되거나 기체 성분 간에 반응을 일으켜 증착하는 과정으로, 높은 온도에서 진행될수록 막 품질이 향상되는 경향이 있습니다. 온도를 높일 수 없는 경우에는 압력을 낮추는 LPCVD(Low Pressure CVD) 또는 플라즈마를 이용한 PECVD(Plasma Enhanced CVD) 등이 사용됩니다.

3.7.4 Epitaxy

Epitaxy는 단결정 위에 동일한 구조의 박막을 성장시키는 과정입니다. 단결정 기판 표면에 고온에서 동일한 구조를 가진 소스를 공급하여 표면에 도착한 원자가 결정 격자 패턴을 따라 확장되도록 합니다. 이로써 단결정 위에서만 성장하기 때문에 산화막 Pattern을 이용하여 선택적 Epitaxy 과정을 수행할 수 있습니다.

3.8.1 상호 연결

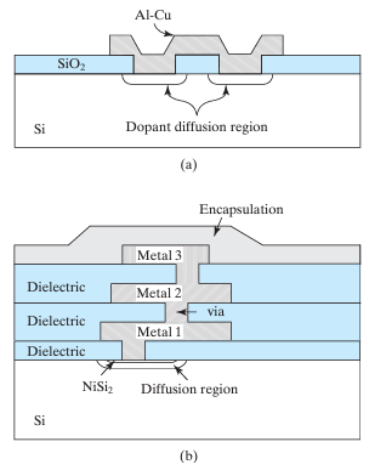

반도체 소자는 상호 연결되어야 하며, 이는 금속선을 통해 이루어집니다. 전압, 전류의 공급 또는 전기 신호 전달을 위해 금속선을 연결하는 프로세스를 Metalization이라고 합니다. 반도체 Chip 기술의 발전으로 일반적으로는 다층 금속 구조가 사용됩니다.

인접한 금속층은 서로 단락이 나지 않도록 유전체 층에 의해 분리되어 있습니다. 금속화된 금속은 초기에는 주로 알루미늄(Al)이 사용되었습니다. 알루미늄은 높은 비저항을 가지지만, 전자이동 현상(Electromigration)에 의한 신뢰성 문제가 있습니다. 알루미늄 원자들이 전기장 방향으로 이동하면서 발생하는 Void나 Hillock과 같은 결함으로 인해 금속선의 저항이 증가하거나 끊어질 수 있습니다.

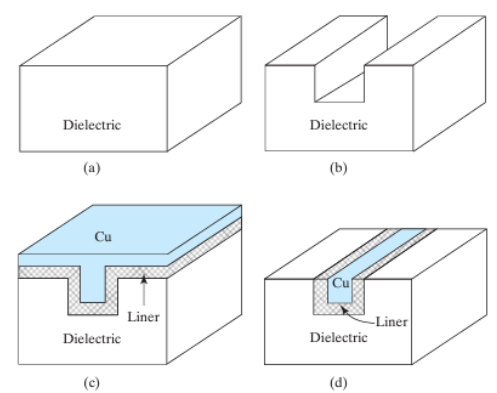

이에 대한 대안으로 구리(Cu)가 도입되었습니다. 구리는 알루미늄보다 Electromigration에 대한 신뢰성이 우수하며 낮은 저항을 갖습니다. 구리는 도금 및 화학 기상증착(CVD)으로 증착될 수 있으며, Dry Etching이 어려워 Damascene 공정에 사용됩니다.

Damascene 공정은 Photolithography로 Pattern을 형성하고, 그 위에 구리를 증착한 후 CMP 공정으로 폴리싱하여 패턴된 구리를 만듭니다. 구리는 유전체에서 빠르게 확산하므로 TiN과 같은 물질이 유전체 사이에 증착됩니다. 금속층 간에 있는 유전체는 일반적으로 SiO2가 사용되지만, 유전률이 낮은 저유전체(low-k) 물질이 사용될 수 있습니다.

유전 상수 k가 낮아야 Capacitance가 작아지며, Capacitance가 높으면 RC Delay를 증가시켜 회로 속도를 감소시키고, 전력 소모를 높이며, 이웃하는 도체 선 간의 간섭을 일으킬 수 있습니다. 이러한 Metal Line 및 Metal Contact을 만드는 프로세스를 Back End Process라고 합니다.

3.9.1 테스팅, 조립 그리고 검정

반도체 공정이 마무리되면 제품이 양산에 적합한지, 그리고 정상 작동하는지 확인하기 위해 전기적 테스트가 수행됩니다. 이를 Electrical Die Sorting(EDS)이라고 합니다.

테스트를 통과하지 못한 칩은 표시가 되어 조립되지 않습니다. EDS를 통과한 칩들은 Sawing(절단)되어 플라스틱이나 세라믹 패키지로 조립되거나, 직접적으로 회로 보드에 부착될 수 있습니다. 단일 칩으로 사용되는 경우도 있지만 대부분은 멀티 칩으로 Stacking되기도 합니다.

칩과 패키지 간의 전기적 연결은 주로 자동화된 Wire Bonding이나 Solder Bump를 사용하여 이루어집니다. Wire Bonding은 Wire를 사용하여 패키지와 칩을 연결하는 방식이며, Solder Bump는 Wire 대신에 칩과 패키지의 금속 패드를 정렬하여 연결하는 방식입니다.

칩이 Multi Stacking될수록 많은 Wire가 필요하고, Wire가 길어질수록 전기 저항이 증가합니다. 반면, Solder Bump는 칩과 패키지를 직접 연결하므로 Wire보다 전기적 저항 면에서 우수하며, 공간 활용도도 높습니다.

패키지 조립 후 제품이 출하되기 전에 추가적인 테스팅이 진행됩니다. 제품의 신뢰성은 오랜 기간에 걸친 수명 테스트와 수천 개의 생산 샘플에 대한 검증(Qualification) 과정을 통해 입증됩니다.

'Semiconductor' 카테고리의 다른 글

| 전자와 정공의 결합 모델(Motion and Recombination of Electrons and Holes) (2) | 2024.06.07 |

|---|---|

| 반도체 내의 전자와 정공(Electrons and Holes in Semiconductor) (1) | 2024.06.03 |